Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

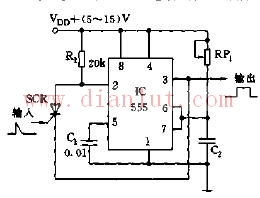

As shown in the figure, 555 and R1, RP1, C2, etc. constitute a trigger delay circuit. Normally, since R1 is connected to VDD, 555 is in the reset state, that is, the 3 pin is at a low level; when the trigger signal arrives, the SCR is turned on, and the 2 pin has a low level signal, so that the 555 is inverted and the output is high. The temporary stability width is τ=1.1RP1C2. After triggering, the SCR is turned off. This circuit reduces the need for trigger pulses. If the CMOS type 555 (or 556) is used, the trigger current can also be reduced.

August 12, 2024

Mail a questo fornitore

August 12, 2024

August 14, 2023

January 07, 2021

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.